I've been learning about FPGA devices... recording my thoughts, experiences, and technical notes here on this blog. In the span of just a few weeks - two different devices caught my attention. One is the

Numato Mimas V2 Spartan 6 FPGA Development Board with DDR SDRAM complete with audio, video, SD slot, 7-segment display, on-board LEDs, and more... for about 50 bucks.

|

| Numato Mimas-V2 FPGA Development Board with demo code running |

The other is the old, now obsolete but excellent new learning opportunity

Pano Logic zero client that happen to also have a Xilinx(TM) chip on board:

In particular, Tom Verbeure has these impressive

Pano Logic Zero Logic G1 and

G2 GitHub repositories (see also

this Hackaday project).

Last year, I bought one of those Altera Cylone IV boards on ebay, and wrote a little

blog about it. Setup was a long and tedious process. I never ended up doing much with that board.

More recently - I've been tinkering with the Lattice iCE40 chips, such as the one found in the awesome

tinyFPGA BX board and the somewhat rare but much more feature-rich

ULX3S board (which is also in the running to hopefully take first place in the

Hackaday Contest, vote for it

here). I'm also awaiting my first

iCEBreaker board from

1bitsquared that certainly looks interesting.

I have several blog posts on the iCE40 FPGA, including

using the tinyFPGA on WSL, loading up a soft

RISC-V on the tinyFPGA, and more recently some ULX3S topics:

first day more on

using WSL, some

samples and walk-through examples and most recently my

AD/DA with the ULX3S.

In addition to proprietary vendor tools - I've been using

yosys &

nextpnr open source FPGA programming tools. The community is really awesome, with people impressively helpful and patient despite my sometimes clearly newbie questions. Although I have a background in Electronic Engineering, I work at the Day Job as a Senior Software Engineer (mainly C#, SQL). Learning FPGA is something I've wanted to do for quite some time. This has been quite a humbling and interesting experience.

Certainly one of the interesting topics related to FPGA programming is Formal Verification. I've been reading a lot about this, but many of the examples have been with quite complex systems. Fortunately

@zipcpu published

An Exercise in using Formal Induction: a small and focused walk-though that illustrates the concepts of Formal Verification with a relatively simple FPGA shift register.

I've had some reservations about the Xilinx chips - not the least concern of which was the story earlier this year where

Xilinx sent lawyers after online educators. Additionally, their

Vivado software costs thousands of dollars, making the kitchen-table learning experience quite a bit less desirable. Still, one cannot deny they are a major player in the FPGA world. Despite the

sharp drop on April 24/25 - their stock appears to still be

doing well over the course of the last year. Further, the

SPARTAN-6 chips do not require Vivado (glad I learned that before downloading the full 18+ gig app! )

"Spartan-6 needs ISE, not Vivado - Vivado is only for 7-series and newer"

-- @fpga_dave

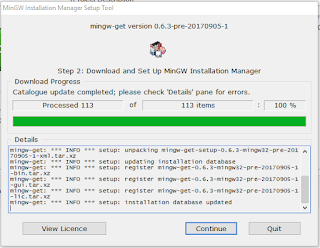

I'm downloading the

ISE which is considerably smaller, but still gigs in size. Any discussion on the ISE should certainly include this

blog on Installing Xilinx ISE inside a Docker Container. I think I'll try a normal install before venturing into Docker territory.

Further, the Xilinx chips do not seem to be supported by the open source

yosys &

nextpnr the way the iCE40 chips are. So it appears we are locked in to proprietary vendor tools for the Spartan-6 FPGA development.

The MimasV2 board has a Xilinx

SPARTAN XC6SLX9 CSG324 FPGA, which appears to be the second-to-lowest-end device with 9,152 logic cells and 106 user IOs. Still, this is probably more than adequate for a learning / development board.

|

| Excerpt from Xilinx(TM) Spartan-6 Family Overview PDF |

My first experience with latest ISE was really horrible. The "Windows version" is actually an Oracle VirtuaBox linux VM. The Xilinx software might be ok, but the VM in which is runs is not cool. Perhaps I am just used to the clean and effective VM machines provided by the folks at VMWare. But in my case, the mouse controls were simply horrible & lagged. The keyboard control is wonky: hold down the right-ctrl key. I am right handed, my right hand is usually on the mouse; super annoying to switch between the VM and my host. The list goes on. (Update: after a Windows reboot, the laggy mouse in the VirtualBox seems to have been resolved. Other operations are still wonky)

In short, I highly recommend an older version of the ISE to run natively on Windows. The official version that was supported was Windows 7. So ymmv in Windows 10. I'm using the

13.1 version (Update - There's a non-VM version 14.7 of the ISE) that can be downloaded from the

Xilinx archive. Yes, you'll need an account to login and the free license will still be node-locked to your MAC address. Some of the ebay vendors include a disk with software.

UPDATE: It appears that the VirtualBox version was probably created because of an apparent problem with JTAG drivers in Windows 10, given an "The Platform Cable USB is not detected" error like this:

Enumerating cables. Please wait.

PROGRESS_START - Starting Operation.

Connecting to cable (Usb Port - USB21).

Checking cable driver.

Source driver files not found.

The Platform Cable USB is not detected. Please connect a cable.If a cable is connected, please disconnect

and reconnect to the usb port, follow the instructions in the 'Found New Hardware Wizard', then retry

the Cable Setup operation.

PROGRESS_END - End Operation.

Elapsed time = 1 sec.

I found that running iMPACT as Administrator in Windows solved this problem for me:

|

| Run iMPACT as Administrator to resolve USB JTAG device problems. |

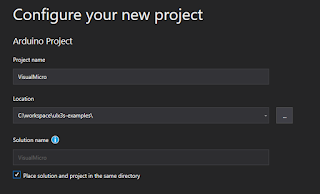

There are a bunch of apps that get installed with the Xilinx software. The development environment of interest is the ISE, listed under either 32bit or 64bit "Project Navigator". Although I have a 64 bit machine, the 32 bit software seemed to be more reliable.

If you try to open a

Xilinx project file such as the Numato demo, and the ISE just blinks and exits, it may be because the project file was created with a newer version. I found that simply editing the project file with your favorite text editor seems to work. Edit the version here:

|

| xise version setting |

If the ISE still exits immediately when double-clicking on an xise file, then the 64-bit version is probably launching. When I launch the 32 bit version, then manually open the xise project file, all seemed to go much more smoothly. I'm not sure why the 64 bit version is unhappy on my 64 bit Windows 10.

Numato has a

bunch of sample code on GitHub, including the

demo source code and an interesting

HDMI driver. Here, I'm looking at the project demo in:

./FPGA/MimasV2/mimasV2Demo/mimasV2Demo.xise

The Numato sample code

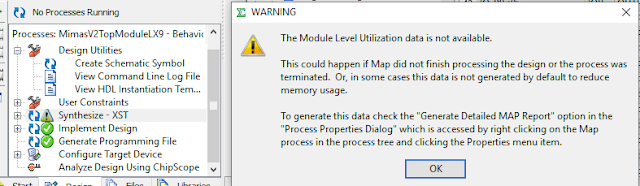

README indicates that to create a binary file in the ISE:

Right click on the "Generate Programming Files" process in the process window and select "Rerun all".

That's great - if you can find the "Generate Programming Files":

|

| By default, the "Generate Programming Files" is not visible. |

In order to actually create the binary file, click on the MimasV2TopModuleLX9 filename in the Hierarchy window, then the Generate Programming Files will appear in the lower pane:

Unlike Visual Studio, that indicates at compile time where the binary files are... there was no indication in the ISE where the bit and bin files ended up. They ended up in the same directory as the xise file. Perhaps not exactly the best organization of files, but at least easy to find:

|

| MimasV2 sample code bin and bit files. |

The bin and bit files are different sizes. I used the bin file.

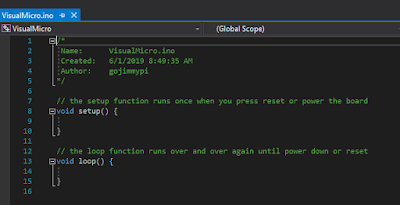

Poking around at things, I saw this message when clicking on "Module Level Utilization":

I read that about 5 times while trying to find where, exactly it was referring to. I'm glad I saved the snip of that, as after closing it, future clicks on the "Module Level Utilization" no longer gave the information.

The actual location is found under "Implement Design". Right-click on "Map" and select "Process Properties":

Then check this box:

Re-run the Map (right click, re-run)... and indeed the Module Level Utilization is now available:

One thing in particular to the ISE newbie, is how to actually get binary data onto the FPGA. Tools - Program? No, of course not. There's something called "iMPACT" that is used for that. :/ Clearly someone needs to hire a better UI/UX expert.

Before attempting to program the Numato board, ensure Windows has the proper USB drivers installed. Although Windows will try to auto-install drivers for the Numato board, custom drivers are needed. This too can be downloaded from the Numato site

here. Curiously, the Numato drivers are only two small files: a cat and inf.

Note that several times after bringing my computer out of sleep mode, Windows 10 would "forget" the drivers for the Numato board and give a warning on how a USB device is configured properly. Simply unplugging and re-plugging the USB cable seems to resolve this. Device manager should show something like this:

The folks at Numato have put together a quite nice

Mimas-2 Getting Started Walk-Through that is really quite helpful. The article is clean, clear and well written.

The

Numato Walk-Thru has a section on

Configuring MIMAS V2 Using Configuration Tool. This tool is vastly easier and more intuitive to get up and running with code on their FPGA board. Clearly they realized that the ISE iMPACT was a bit wonky, and created their own, easy-to-upload

applet. They should have included a link to that in the walk-through. Still, it was easy to find by clicking on the "downloads" link on the

MimasV2 Product Page. This makes flashing firmware onto the Numato FPGA board a breeze:

|

| Numato Mimas V2 Config tool uploading binary code to FPGA flash. |

My only suggestion might be to make it open source, and/or provide a command-line version. It also might have been nice to limit the com port selection to those actually found on the computer. The most important thing is that it works: simple to use and seems to work well.

If for some reason the sample code does not run properly. Numato provides a

sample bin file on the download page.

I did purchase a JTAG FPGA Programmer from ebay, like

this one. Some vendors sell a CD with the software. This is certainly handy if you don't want to download gigs of software. You'll still need to get a license file from the Xilinx web site. Note that the Numato board

can be programmed with a JTAG device, but does not

require one.

In looking at the Pano devices, such as the

G2 from Tom Verbeure, the first thing to do is get rid of the dash in the filename. Otherwise the ISE will complain about "The directory path is not valid and cannot be used"

Navigate to the blink\ise directory and open the ise.xise file:

Disclosure: I am not affiliated with any of the entities mentioned in this blog. All opinions are my own and do not reflect that of my employer. The kind folks at Numato sent me a free Mimas-2 board stating: "

in exchange of a small publication of your thoughts about it on your website". I was not compensated in any other way.

Xilinx(TM) are is a registered trademark of

Xilinx. Content in this blog is purely my personal experience and is in no way related to Xilinx the company, or any other organization. I am not endorsing or recommending for or against any product. For more Xilinx legal information see

this link.

Resources, Inspiration, Credits, and Other Links: